# SoK: Analysis of Accelerator TEE Designs

Chenxu Wang¹\*†‡, Junjie Huang¹†, Yujun Liang†, Xuanyao Peng†¶, Yuqun Zhang†,

Fengwei Zhang†\*⊠, Jiannong Cao‡, Hang Lu¶, Rui Hou§¶, Shoumeng Yan∥⊠, Tao Wei∥ and Zhengyu He∥

\*Research Institute of Trustworthy Autonomous Systems, Southern University of Science and Technology, China

†Department of Computer Science and Engineering, Southern University of Science and Technology, China

†Department of Computing, The Hong Kong Polytechnic University, China

§State Key Laboratory of Cyberspace Security Defense, IIE, Chinese Academy of Sciences, China

¶University of Chinese Academy of Sciences, China,

∥Ant Group, China

Abstract—Accelerator trusted execution environment (TEE) is a popular technique that provides strong confidentiality, integrity, and isolation protection on sensitive data/code in accelerators. However, most studies are designed for a specific CPU or accelerator and thus lack generalizability. Recent TEE surveys partially summarize the threats and protections of accelerator computing, while they have vet to provide a guide to building an accelerator TEE and compare the pros and cons of their security solutions. In this paper, we provide a holistic analysis of accelerator TEEs over the years. We conclude a typical framework of building an accelerator TEE and summarize the widely-used attack vectors, ranging from software to physical attacks. Furthermore, we provide a systematization of accelerator TEE's three major security mechanisms: (1) access control, (2) memory encryption/decryption, and (3) attestation. For each aspect, we compare varied security solutions in existing studies and conclude their insights. Lastly, we analyze the factors that influence the TEE deployment on real-world platforms, especially on the trusted computing base (TCB) and compatibility issues.

## I. Introduction

Trusted execution environment (TEE) is a popular and widely used security mechanism to ensure data confidentiality and integrity on today's platforms. Over the past two decades, the industry and academy propose various TEE designs and hardware supports on both cloud platforms [1], [2] and mobile devices [3], supporting general and state-of-the-art requirements such as data storage [4]–[7], machine learning [8]–[10], and blockchain applications [11]–[13]. These designs provide isolated computing environments and secure CPU resources for users, protecting the sensitive data storage and computing from the untrusted software components.

Currently, extending TEEs from CPU to other accelerator devices, such as Graphics Processing Units (GPUs) [14]–[18], Neural Processing Units (NPUs) [19]–[22], Tensor Processing Units (TPUs) [23], Field Programmable Gate Arrays (FPGAs)

performance computing on their sensitive tasks and enjoy the benefits of strong confidentiality, integrity, and isolation. Nevertheless, there is no standard criterion for building an accelerator TEE. Studies propose a large number of accelerator TEE designs, ranging from large-scale clouds [28]-[30] to lightweight endpoints [31]–[33], from traditional Intel platforms [34], [35] to the new RISC-V architecture [36], [37]. Unfortunately, directly applying one accelerator TEE design to a different platform can be challenging due to the variance in CPU and accelerator architecture. Recent TEE surveys partially analyze security computing on GPU [8] and FPGA [38]. They also provide a security framework and concerns on CPU-side TEEs [39]-[41]. However, there is an absence of a systematic analysis of the accelerator TEE framework, potential threats to mainstream security solutions. and a discussion of the pros and cons of deploying these TEEs in real-world platforms.

[24]–[26], and other accelerators [27], is gradually popular.

By using accelerator TEEs, users securely perform high-

To address this problem, we provide a holistic analysis of accelerator TEEs. Our analysis answers the primary question: **RQ1:** What is the typical framework of building an accelerator TEE? We survey the state-of-the-art accelerator TEEs in the past decade (detailed in §II). Based on this, we categorize accelerator TEEs into three types: (1) *Host-type*, which mainly protects accelerators with CPU-side software/firmware; (2) *Acc.-type*, which prefers to design their protection on accelerators and the connection I/O bus; and (3) *Mix-type*, which is a mixed design of these two types. We detail our categorization in §III. Despite the CPU architecture, accelerator devices, and platforms' variance, accelerator TEEs follow the aforementioned types to deploy security protection.

Since we categorize accelerator TEEs and summarize their design features, our study focuses on a further question: **RQ2:** How to build an accelerator TEE with ensuring strong security on varied CPU/accelerator? To answer this question, we summarize the widely-used attack vectors in the typical accelerator TEE framework (detailed in §IV). Attacks on accelerator TEEs can vary from CPU-side application to privileged hypervisor, from software to physical attacks. Based on the attack vectors, we summarize three major defense mechanisms against the powerful adversary: (1)

<sup>&</sup>lt;sup>1</sup>Chenxu Wang and Junjie Huang are co-first authors.

<sup>&</sup>lt;sup>™</sup>Fengwei Zhang and Shoumeng Yan are corresponding authors.

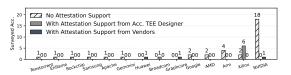

access control, (2) memory encryption, and (3) attestation, then provide a detailed solution categorization for each mechanism. Besides categorization, we provide several insights for each mechanism. For access control, we focus on summarizing the solutions (and their combination) preference on the three types of accelerator TEE (i.e., *Host-type*, *Acc.-type*, and *Mix-type*). For memory encryption, we find that many studies lack such a security solution and cannot defend against physical threats. We analyze the significant overhead problems in existing memory encryption designs due to the traditional solution migration and inconsistent granularity. For attestation, we summarize the generic attestation workflow for accelerator TEE. Based on this, we find that most solutions lack the essential security supports to ensure attestation correctness. For the aforementioned security mechanisms, we detail our analysis and insights in §V, §VI, and §VII, respectively.

Lastly, for deploying accelerator TEEs on real-world devices, we focus on another question: **RQ3:** What factors influence the accelerator TEE deployment on real-world platforms? With the sharp increase in accelerator applications, however, accelerator TEEs have yet to be widely applied in real-world platforms. We consider two major aspects: large TCB and low compatibility. Specifically, we analyze the TCB size of the guest and system side for each accelerator TEE (detailed in §VIII) and provide a compatibility analysis (detailed in §IX). Our analysis shows that most accelerator TEEs have non-trivial TCB requirements and non-negligible compatibility issues. This influences the deployment of accelerator TEEs and should be carefully addressed in future TEE designs.

We summarize our contributions as follows:

- We summarize current design choices of accelerator TEEs into three main classifications: *Host-type*, *Acc.-type*, and *Mix-type* designs.

- We describe attack vectors and their capabilities for accelerator computing. This model benefits TEE designers in terms of defending against specific attacks.

- We summarize the mainstream solutions on access control. We also analyze the preference for solutions and their combination in existing studies.

- We categorize the solutions for memory encryption. We compare these solutions' pros and cons on granularity, security guarantee, and performance aspects.

- We analyze existing solutions in attestation, with a detailed attestation workflow and the lacking components of existing studies.

- We analyze the TCB size in existing studies. Our analysis indicates security concerns of increasing guest/system TCB in accelerator TEE designs.

- We comprehensively discuss compatibility issues across existing studies, especially in multi-type and plug-andplay support on software/hardware.

## II. METHODOLOGY

We perform a literature review focusing on the research studies about accelerator computing protection with TEE technology. Following the state-of-the-art [38], [83], [84], we

Table I: Overview of the analyzed accelerator TEEs.

| Acc. TEE            | Year | Pub.       | Host CPU         | Acc.         | Src. | CPU TEE |

|---------------------|------|------------|------------------|--------------|------|---------|

| Graviton [34]       | 2018 | OSDI       | Intel            | GPU          | 0    | •       |

| HIX [33]            | 2019 | ASPLOS     | Intel            | GPU          | 0    | •       |

| HETEE [28]          | 2020 | S&P        | Any <sup>2</sup> | General Acc. | 0    | 0       |

| TrustOre [42]       | 2020 | CCS        | Intel            | FPGA Acc.    | Ō    | ě       |

| Telekine [43]       | 2020 | NSDI       | Intel            | GPU          | Õ    | •       |

| Ambassy [44]        | 2021 | TMC        | Arm              | U-FPGA Acc.  | 0    | •       |

| CommonCounters [45] | 2021 | HPCA       | Intel            | GPU          | 0    | •       |

| CURE [36]           | 2021 | USENIX     | RISC-V           | U-Acc.       | 0    | •       |

| PSSM [46]           | 2021 | ICS        | Intel            | GPU          | Ó    | •       |

| SGX-FPGA [35]       | 2021 | DAC        | Intel            | FPGA Acc.    | 0    | •       |

| Cronus [47]         | 2022 | MICRO      | Arm              | General Acc. | •    | •       |

| GuardNN [48]        | 2022 | DAC        | Any <sup>2</sup> | DNN Acc.     | 0    | 0       |

| LEAP [49]           | 2022 | TMC        | Arm              | U-GPU        | Ō    | •       |

| LITE [50]           | 2022 | ICS        | Intel/AMD        | GPU          | 0    | •       |

| MGX [51]            | 2022 | ISCA       | Intel            | DNN Acc.     | 0    | •       |

| ShEF [52]           | 2022 | ASPLOS     | Any <sup>2</sup> | FPGA Acc.    | •    | 0       |

| StrongBox [31]      | 2022 | CCS        | Arm              | U-GPU        | •    | •       |

| TNPU [53]           | 2022 | HPCA       | Intel            | U-NPU        | 0    | •       |

| SHM [54]            | 2022 | HPCA       | Intel            | GPU          | 0    | •       |

| RME-DA [55]         | 2023 | (Industry) | Arm              | General Acc. | 0    | •       |

| SEV-TIO [56]        | 2023 | (Industry) | AMD              | General Acc. | 0    | •       |

| TDX Connect [57]    | 2023 | (Industry) | Intel            | General Acc. | 0    | •       |

| H100 [58]           | 2023 | (Industry) | Intel/AMD/Arm    | GPU          | Ō    | •       |

| AccShield [59]      | 2023 | DAC        | Intel/AMD        | TPU          | 0    | •       |

| AvaGPU [32]         | 2023 | CCS        | Arm              | U-GPU        | •    | •       |

| GR-T [60]           | 2023 | EuroSys    | Arm              | U-GPU        | •    | •       |

| Honeycomb [61]      | 2023 | OSDI       | AMD              | GPU          | 0    | •       |

| ITX [62]            | 2023 | ATC        | Any <sup>2</sup> | IPU          | 0    | 0       |

| MyTEE [63]          | 2023 | NDSS       | Arm              | U-GPU        | •    | •       |

| Plutus [64]         | 2023 | HPCA       | Any <sup>2</sup> | GPU          | 0    | 0       |

| SAGE [65]           | 2023 | ATC        | Intel            | GPU          | •    | •       |

| Securator [66]      | 2023 | HPCA       | $Any^2$          | U-NPU        | 0    | 0       |

| ACAI [67]           | 2024 | USENIX     | Arm              | General Acc. | •    | •       |

| CAGE [68]           | 2024 | NDSS       | Arm              | U-GPU        | •    | •       |

| Dhar et al. [30]    | 2024 | ACSAC      | Any <sup>1</sup> | General Acc. | 0    | •       |

| HyperTEE [69]       | 2024 | MICRO      | RISC-V           | U-DNN Acc.   | 0    | •       |

| Na et al. [70]      | 2024 | HPCA       | Intel            | GPU          | Ō    | •       |

| Salus-GPU [71]      | 2024 | HPCA       | Any <sup>2</sup> | GPU          | Ó    | 0       |

| Salus-FPGA [72]     | 2024 | ASPLOS     | Intel            | FPGA Acc.    | 0    | •       |

| sIOPMP [73]         | 2024 | ASPLOS     | RISC-V           | U-DNN Acc.   | 0    | •       |

| sNPU [37]           | 2024 | ISCA       | RISC-V           | U-NPU        | 0    | •       |

| SrcTEE [74]         | 2024 | TC         | Arm              | U-FPGA Acc.  | 0    | •       |

| T-Edge [75]         | 2024 | ACSAC      | Arm              | U-FPGA Acc.  | •    | •       |

| TensorTEE [76]      | 2024 | ASPLOS     | Intel            | NPU          | 0    | •       |

| ASGARD [77]         | 2025 | NDSS       | Arm              | U-NPU        | •    | •       |

| ccAI [78]           | 2025 | MICRO      | Any <sup>1</sup> | General Acc. | 0    | •       |

| GuardAIn [29]       | 2025 | S&P        | Any <sup>2</sup> | NPU          | 0    | 0       |

| PipeLLM [79]        | 2025 | ASPLOS     | Intel/AMD        | GPU          | 0    | •       |

| Portal [80]         | 2025 | S&P        | Arm              | U-GPU        | 0    | •       |

|                     | 2025 | DAC        | Any <sup>2</sup> | DNN Acc.     | •    | 0       |

| SeDA [81]           | 2023 | DAC        | Ally             | DININ ACC.   | ŏ    |         |

<sup>&</sup>lt;sup>1</sup>It relies on CPU TEE with memory encryption support. <sup>2</sup>It adapts any CPU architecture with/without CPU TEE.

collect research studies from Google Scholar<sup>1</sup>, a mainstream search engine that indexes most research studies from digital libraries (e.g., ACM Digital Library<sup>2</sup>, IEEE Xplore<sup>3</sup>, Arxiv<sup>4</sup>). To use this search engine, we first perform a search query with two sets of keywords — accelerator devices (e.g., GPU, NPU, TPU, DPU, IPU, ASIC, FPGA and xPU) and TEE technology (e.g., TEE, Confidential Compute, and architecture-specific TEEs such as Arm TrustZone and Intel SGX). This results in more than 20K studies, while our search stops at the 200th study — most studies after this are irrelevant to our study. For these studies, we consider two criteria to filter our target studies:

- Academic or industry studies should leverage at least one TEE-based security mechanism (e.g., Intel SGX [1], Arm CCA [85], or customized hardware [58]) to protect the computing environment of at least one accelerator.

- Academic studies should provide a detailed defense mechanism on the accelerator computing workflow rather than protecting I/O for generic devices.

These criteria help us filter the accelerator TEE studies. To

<sup>1</sup>https://scholar.google.com

<sup>&</sup>lt;sup>2</sup>https://dl.acm.org

<sup>&</sup>lt;sup>3</sup>https://ieeexplore.ieee.org/

<sup>4</sup>https://arxiv.org

extend our paper collection, we also perform forward/backward searching on these studies (i.e., searching studies that refer to and are referred). Overall, we analyze 51 studies, which are selected from top-level conferences and mainstream industry designs, and report them in Table I. We extensively discuss our observations and relevant insights as follows.

## A. Motivation

Accelerator TEE study is popular but not systematic. In the past three years, accelerator TEEs have gradually attracted the public's attention and have sharply increased. As shown in Table I, 41/51 studies, including four industry studies [55]–[58], have been proposed since 2022. However, compared with the CPU TEE with a long history (e.g., Arm TrustZone [3] in 2004), the formal study of accelerator TEE only begins in 2018 [34]. In addition, designs of accelerator TEEs heavily rely on CPU TEEs (42/51 studies) and have yet to summarize a unique design framework. Based on this, our paper needs to address a primary problem: RQ1: What is the typical framework of building an accelerator TEE?

Analyzing accelerator TEE is challenging. Studies on accelerator TEEs are exploring various CPU-accelerator combinations. Currently, we find more than ten CPU-accelerator combinations in accelerator TEE designs — Accelerator TEEs protect various accelerators (e.g., GPU and NPU) that run with different accelerator computing workflows and are equipped on various CPU hosts (e.g., Arm, Intel, and RISC-V). Most accelerator TEEs prefer to be compatible with x86-based (i.e., Intel and AMD) platforms (32/51 studies) and support GPU computing (30/51 studies). This is because x86-based platforms and GPUs are the mainstream heterogeneous systems for high-performance computing. In addition, we observe that studies for Arm-based accelerator TEEs prefer to support unified-memory accelerators (11 studies). The major reason is that most Arm-based platforms are endpoints and support embedded accelerators. For RISC-V accelerator TEEs, 3/4 studies prefer to support configurable NPU or DNN accelerators. Due to the complex accelerator TEE implementation, we propose the second question: RQ2: How to build an accelerator TEE while ensuring strong security on varied CPU/accelerator? Accelerator TEEs have yet to be widely deployed. Clouds and endpoints gradually support multiple types of accelerators to work together on various accelerator tasks. However, most accelerator TEEs target specific CPU-accelerator combinations (43/51 studies). We observe that 40/51 studies support a specific CPU architecture, and 43/51 studies are only designed for one type of accelerator device. Considering that different CPUs and accelerators are largely varied in security and functionality, we worry that most accelerator TEEs have yet to support a generic accelerator computing environment. Worse, only a few accelerator TEEs (12/51 studies) release their source code. It is challenging to migrate accelerator TEE research to different platforms. We raise the third research question: RQ3: What factors influence the accelerator TEE deployment on real-world platforms?

## III. OVERVIEW

# A. System Model

Accelerator TEE definition and requirements. Compared to traditional CPU TEEs (e.g., Intel SGX [1] and Arm Trust-Zone [3]), accelerator TEEs extend protection to accelerator devices while ensuring the security goals of confidentiality, integrity, and authenticity. During the accelerator task preparation, computation, and termination phases, TEE-related components must secure two key elements: (1) Accelerator workloads, including input/output data, model parameters, task code (e.g., AI models), page tables, and other confidential metadata; and (2) the accelerator environment, such as the hardware status of both the CPU and accelerator. Beyond these primary security guarantees, accelerator TEEs can also provide additional security support (e.g., protecting entire software stacks) while minimizing influences on accelerators (e.g., maintaining compatibility and performance).

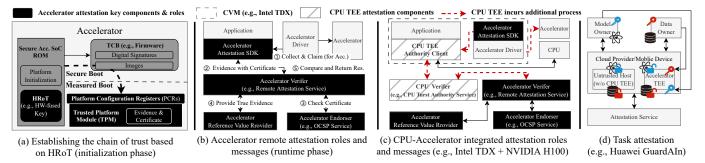

CPU side. Accelerator TEEs, which are deployed on the mainstream architectures (e.g., x86, Arm, and RISC-V), follow a generic architecture layout on the CPU side. Generally, the CPU side software consists of three major components: (1) a host running a hypervisor and host OS, (2) a CC (i.e., confidential computing) environment running a TSM (i.e., TEE Security Manager [86]) and several confidential virtual machines (CVMs) or enclaves [87] [2] [88], and (3) a firmware layer running the highest privilege software (e.g., a monitor [88] [3]). The host and CC environment are strictly isolated with security hardware support (e.g., Arm TZASC in TrustZone [3]), which can be configured by monitor or TSM. Accelerator side. We summarize the mainstream accelerator or extension hardware design for accelerator TEEs. First, an accelerator delegated to different workloads must equip a compute engine (including computing units, registers, caches, and other computing resources) to process workloads. Moreover, accelerators with security supports additionally provide three components: (1) the encryption module (e.g., AES-GCM engine in Microsoft ITX [62]) for security communication and memory protection, (2) the attestation module for attestation, such as the Hardware Root-of-Trust (HRoT) in NVIDIA H100 [58], and (3) the security controller (e.g., Task Scheduler in GuardAIn [29]) for TEE management. For accelerator memory, several accelerators (e.g., NVIDIA [58] and AMD GPUs [15]) own a physically isolated memory (e.g., GDDRx [45]) while others (e.g., Arm GPUs [89]) share the main memory with CPU and other peripherals.

#### B. Accelerator TEE Categorization

Categorizing the surveyed accelerator TEEs can be challenging since they are implemented on different platforms (i.e., various CPU-accelerator combinations) with different security mechanisms, and require different levels of software/hardware changes. Nevertheless, based on our observations, these accelerator TEEs still require system control components to coordinate different security mechanisms for accelerator confidential computing. Thus, based on the position of the modified

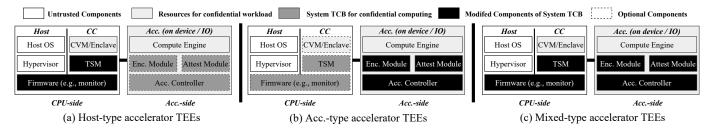

Figure 1: Architecture overview of the Host-type, Acc.-type, and Mix-type accelerator TEEs.

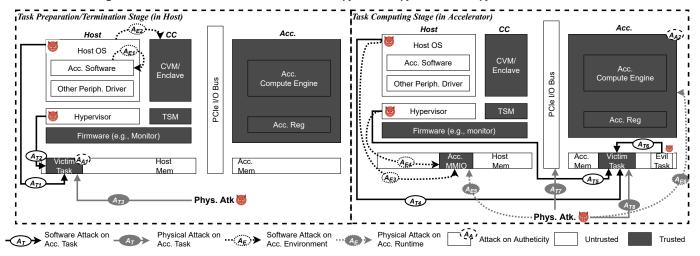

Figure 2: Attack vectors of accelerator computing.

system control components, we classify these accelerator TEEs into three categories: *Host-type* designs, *Acc.-type* designs, and *Mix-type* designs. Figure 1 shows a brief architecture overview of these three designs. Moreover, we provide detailed components of different accelerator TEE types in Table II. In this table, we categorize the selected studies into three types (i.e., *Host-type*, *Acc.-type*, and *Mix-type*) and show the security components related to accelerator TEE (i.e., CVM/enclave, TSM, firmware, encryption module, attestation module, and accelerator controller).

*Host-type* designs. As shown in Figure 1(a), *Host-type* designs modify privileged CPU-side system control components (e.g., the TSM such as RMM [67] [80] or secure monitor [31] [68]) to control accelerator TEEs and leverage CPU-assisted protection mechanisms (e.g., Intel SGX [1] and Arm TrustZone [3]) to isolate, attest, and secure the accelerator computing environment. During the trusted accelerator computing, the key role of the system control component is to ensure the data path and interaction between the TEE on the host and the accelerator hardware, preventing data leakage from untrusted software (e.g., OS and hypervisor) and devices. Since CPU-side hosts generally implement mature security mechanisms, most Hosttype designs directly leverage these mechanisms in access control (e.g., Intel EPC [1], Arm TZASC [90]/GPC [91]) and memory encryption (e.g., Intel TME [87], AMD SME [2]), without additional hardware changes on host or accelerator devices. However, several designs still implement customized security primitives (e.g., bus filters in CURE [36] and SGX extensions in HIX [33]).

Acc.-type designs. Compared to the Host-type designs, the Acc.-type designs migrate the accelerator TEE control logic into accelerator (e.g., the command processor [34] [43] in GPUs) or extension hardware (e.g., the security controller [28] [30] between host and accelerator), instead of preserving it in CPU side (see Figure 1(b)). This accelerator controller receives and controls data/command communication from external devices (e.g., the untrusted host [28] [29] or peripherals), manages TEE on accelerator and coordinate security operations (e.g., memory protection via encryption module [53] [51] and environment verification via attest module [58] [62]). The security of the Acc.-type controller is ensured by hardware isolation from the CPU host instead of the privilege software isolation. Thus, most Acc.-type designs unavoidably require hardware modification on accelerator board or extension security hardware, but do not involve host-side hardware changes. These features enable CPU TEE to work orthogonally with Acc.-type designs, such as NVIDIA H100 [58], which supports VM-level CPU TEE [87] [2] [88].

Mix-type designs. Combining the former two, the Mix-type design collaborates the system control components at the CPU and accelerator side to control the accelerator TEE (see Figure 1(c)). In this case, privileged software on the CPU side guarantees the confidentiality and integrity of the communication data, and physical hardware on the accelerator side guarantees the security of the computational data. In this case, privileged software on the CPU side guarantees the confidentiality and integrity of accelerator task submission and termination. In contrast, security hardware on the accelerator

Table II: Design overview of the *Host-type*, *Acc.-type* and *Mix-type* accelerator TEEs.

| Acc. TEE Type                 |                                 | CPU-side            |                              | Accside mo                                           | dules (in Acc./Boar | rd/Ext. IO)                                        |

|-------------------------------|---------------------------------|---------------------|------------------------------|------------------------------------------------------|---------------------|----------------------------------------------------|

| Acc. TEE Type                 | CVM/Enclave                     | TSM                 | Firmware                     | Enc. Module                                          | Attest Module       | Acc. Controller                                    |

| Host-type Acc. TEEs           |                                 |                     |                              |                                                      |                     |                                                    |

| ACAI [67]                     | Arm CCA                         | RMM                 | Monitor                      | PCIe IDE(Acc.)                                       | HRoT(Acc.)          | -                                                  |

| ASGARD [77]                   | Arm TrustZone                   | S-Hyp               | Monitor                      | - 1                                                  | HRoT(Acc.)          | -                                                  |

| AvaGPU [32]                   | Arm TrustZone                   | = "                 | Monitor                      | -                                                    | -                   | -                                                  |

| Cronus [47]                   | Arm TrustZone                   | S-Hyp               | Monitor                      | =                                                    | HRoT(Acc.)          | =                                                  |

| CURE [36]                     | RISC-V Customized               | -                   | M-Monitor                    | -                                                    | -                   | -                                                  |

| CAGE [68]                     | Arm CCA                         | RMM                 | Monitor                      | -                                                    | -                   | -                                                  |

| GR-T [60]                     | Arm TrustZone                   | -                   | Monitor                      | -                                                    | -                   | -                                                  |

| Honeycomb [61]                | AMD SEV-SNP                     | SVSM                | SEV-firmware                 | -                                                    |                     | -                                                  |

| HIX [33]                      | Intel SGX                       | -                   | SGX-firmware                 | -                                                    | HRoT(Acc.)          | -                                                  |

| HyperTEE [69]                 | RISC-V Customized               | -                   | M-Monitor                    | -                                                    | -                   | -                                                  |

| LEAP [49]                     | Arm TrustZone                   | -                   | Monitor                      | -                                                    | -                   | -                                                  |

| MyTEE [63]                    | Arm TrustZone                   |                     | Monitor                      | -                                                    | -                   | -                                                  |

| Portal [80]                   | Arm CCA                         | RMM                 | Monitor<br>M-Monitor         | -                                                    | -                   | -                                                  |

| sIOPMP [73]<br>StrongBox [31] | RISC-V Penglai<br>Arm TrustZone | -                   | M-Monitor<br>Monitor         | -                                                    | -                   | -                                                  |

| XpuTEE [82]                   | Intel TDX/SGX                   | -                   | VMX root                     |                                                      | -                   | -                                                  |

|                               | linei IDA/3GA                   | -                   | VIVIA 100t                   | -                                                    | -                   | -                                                  |

| Acctype Acc. TEEs             |                                 |                     |                              |                                                      |                     |                                                    |

| AccShield [59]                | Intel TDX/AMD SEV               | TDX module/SVSM     | TDX/SEV-firmware             | AES-GCM Engine(Board)                                | HRoT(Board)         | Security Manager(Board)                            |

| Ambassy [44]                  | Arm TrustZone                   | -                   | Monitor                      | AES Cores(Acc.)                                      | -                   | Acc. Controller(Acc.)                              |

| CommonCounters [45]           | Intel SGX                       | -                   | SGX-firmware                 | Opti-Enc. Engine(Acc.)                               |                     | Command Processor(Acc.)                            |

| ccAI [78]                     | _1<br>_1                        | =                   | =                            | AES-GCM Engine(Ext.IO)                               | HRoT(Ext.IO)        | PCIe-SC(Ext.IO)                                    |

| Dhar et al. [30]              | -1                              | -                   | -                            | AES-GCM Engine(Ext.IO)                               | HRoT(Ext.IO)        | Security Controller(Ext.IO)                        |

| GuardAIn [29]                 | -                               | -                   | -                            | AES-GCM Engine(Acc.)                                 | HRoT(Acc.)          | Task Scheduler(Acc.)                               |

| GuardNN [48]                  | - 1 aan                         | -                   | new c                        | Opti-Enc. Engine(Acc.)                               | TTD TO A            | Micro-controller(Acc.)                             |

| Graviton [34]                 | Intel SGX                       | -                   | SGX-firmware                 | AuthEnc/Dec. kernel(Acc.)                            | HRoT(Acc.)          | Command Processor(Acc.)                            |

| HETEE [28]                    | -                               | -                   | -                            | AES-GCM Engine(Ext.IO)                               | HRoT(Ext.IO)        | Security Controller(Ext.IO)                        |

| ITX [62]                      | Intel TDX/AMD SEV               | TDX module/SVSM     | TDX/SEV-firmware             | AES-GCM Engine(Board)                                | CCU(Board)          | ICU(Board)<br>Acc. Controller(Acc.)                |

| LITE [50]<br>MGX [51]         | Intel SGX                       | 1DX module/SVSM     | SGX-firmware                 | Enc. kernel&Spec. HW(Acc.)<br>Opti-Enc. Engine(Acc.) | HRoT(Acc.)          | Control Processor(Acc.)                            |

| Na et al. [70]                | Intel SGX                       | -                   | 3GA-IIIIIwaie                | Opti-Enc. Engine(Acc.)                               | HRoT(Acc.)          | Command Processor(Acc.)                            |

| NVIDIA H100 [58]              | Intel TDX/AMD SEV/Arm CCA       | TDX module/SVSM/RMM | TDX/SEV-firmware/Monitor     | AES-GCM Engine(Acc.)                                 | HRoT(Acc.)          | Acc. Controller(Acc.)                              |

| PipeLLM [79]                  | Intel TDX/AMD SEV/Arm CCA       | TDX module/SVSM/RMM | TDX/SEV-firmware/Monitor     | AES-GCM Engine(Acc.)                                 | HRoT(Acc.)          | Acc. Controller(Acc.)                              |

| Plutus [64]                   | inter rozurano ocazania cert    | -                   | -                            | Opti-Enc. Engine(Acc.)                               | -                   | Memory Controller(Acc.)                            |

| PSSM [46]                     | Intel SGX                       | _                   | SGX-firmware                 | Opti-Enc. Engine(Acc.)                               | _                   | Command Processor(Acc.)                            |

| Salus-FPGA [72]               | Intel SGX                       | _                   | SGX-firmware                 | AES-GCM Engine(Acc.)                                 | HRoT(Acc.)          | SM Controller(Acc.)                                |

| Salus-GPU [71]                | -                               | _                   | -                            | Opti-Enc. Engine(Acc.)                               | -                   | Memory Controller(Acc.)                            |

| Securator [66]                | _                               | -                   | _                            | Opti-Enc. Engine(Acc.)                               | _                   | Security Module(Acc.)                              |

| SeDA [81]                     | -                               | -                   | -                            | Opti-Enc. Engine(Acc.)                               | -                   | Memory Controller(Acc.)                            |

| ShEF [52]                     | -                               | -                   | -                            | Engine set(Board)                                    | HRoT(Board)         | Shield(Board)                                      |

| SAGE [65]                     | Intel SGX                       | -                   | SGX-firmware                 | AuthEnc/Dec. kernel(Acc.)                            | Kernel(Acc.)        | Kernel Caller(Acc.)                                |

| SGX-FPGA [35]                 | Intel SGX                       | -                   | SGX-firmware                 | Enc. Engine(Acc.)                                    | PUF(Acc.)           | FPGA Secure Monitor(Acc.                           |

| SHM [54]                      | Intel SGX                       | -                   | SGX-firmware                 | Opti-Enc. Engine(Acc.)                               |                     | Command Processor(Acc.)                            |

| SrcTEE [74]                   | Arm TrustZone                   | -                   | Monitor                      | AES-GCM Engine(Board)                                | PUF(Board)          | Config. Sec. Unit(Board)                           |

| Telekine [43]                 | Intel SGX                       | -                   | SGX-firmware                 | AuthEnc/Dec. kernel(Acc.)                            | HRoT(Acc.)          | Command Processor(Acc.)                            |

| T-edge [75]                   | Arm TrustZone                   | -                   | Monitor                      | Enc. Engine(Acc.)                                    | HRoT(Acc.)          | Acc. Controller(Acc.)                              |

| TrustOre [42]                 | Intel SGX                       | -                   | SGX-firmware                 | AES-GCM Engine(Acc.)                                 | Attester(Acc.)      | TrustMod(Acc.)                                     |

| TNPU [53]<br>TensorTEE [76]   | Intel SGX<br>Intel SGX          | -                   | SGX-firmware<br>SGX-firmware | Opti-Enc. Engine(Acc.)<br>Opti-Enc. Engine(Acc.)     | -                   | Memory Controller(Acc.)<br>Memory Controller(Acc.) |

|                               | Inci SGA                        | -                   | 3GA-iifmware                 | Opti-Enc. Engine(Acc.)                               | -                   | wiemory Controller(Acc.)                           |

| Mix-type Acc. TEEs            |                                 |                     |                              |                                                      |                     |                                                    |

| Arm RME-DA [55]               | Arm CCA                         | RMM                 | Monitor                      | PCIe IDE(Acc.)                                       | HRoT(Acc.)          | DSM(Acc.)                                          |

| AMD SEV-TIO [56]              | AMD SEV                         | SVSM                | SEV-firmware                 | PCIe IDE(Acc.)                                       | HRoT(Acc.)          | DSM(Acc.)                                          |

| Intel TDX Connect [57]        | Intel TDX                       | TDX module          | TDX-firmware                 | PCIe IDE(Acc.)                                       | HRoT(Acc.)          | DSM(Acc.)                                          |

| sNPU [37]                     | RISC-V Penglai                  | -                   | M-Monitor                    | -                                                    | -                   | Isolator, Guard(Acc.)                              |

<sup>1</sup>It relies on CPU TEE with memory encryption support; DSM: Device Security Manager, a centralized security module in TDISP-compliant device; Acc. The corresponding module is built into the accelerator; Board: Security hardware integrated with accelerators on the same board (e.g., Shield [52]); Ext. IO: External IO security hardware, separate from the accelerator on the same board. (e.g., Security Controller [28], [30]).

side ensures the security of task computation. Currently, there are limited *Mix-type* design efforts (4/51 studies). In these efforts, the TEE Device Interface Security Protocol (TDISP) [86] proposed by PCI-SIG has attracted widespread attention [55]–[57]. Specifically, the Device Security Manager (DSM) on the accelerator side manages one or more TEE Device Interfaces (TDIs) that can be securely assigned to CVMs. The TDISP control path between the DSM and TSM is protected by the trusted channel (i.e., Security Protocol and Data Model [92]), and the data path is protected with the PCI Integrity and Data Encryption (IDE) protocol [93].

Answer to RQ1. As summarized in §III, the framework of accelerator TEEs includes three major types (Host-type, Acc.type, and Mix-type), in which system components can be flexibly configured to meet TEE requirements. Nevertheless, when TEE designers and vendors select a TEE type for implementation, we provide actionable guidelines as follows: First, for most cloud providers (e.g., Aliyun [94]) using commercial accelerators, we recommend designing a Hosttype TEE. Cloud providers can secure accelerator workloads (and even software) within CVMs and implement accelerator environment/hardware protection by modifying the TSM and firmware. Additionally, security components can be easily implemented and upgraded via software patches. Second, for accelerator manufacturers (e.g., NVIDIA [95] and Xilinx [24]), we suggest designing an Acc.-type TEE by integrating controllers, custom encryption IP cores, and attestation modules into the accelerator hardware. With authorization

from TEE users, manufacturers can leverage third-party CVMs to secure their software stacks. Third, for TEE designers/vendors with independent design capabilities (e.g., Apple [18], Huawei [96]), we recommend a *Mix-type* TEE. In this design, TEE designers/vendors can combine modifications to CPU-side TSM/firmware and accelerator hardware to achieve robust, custom-built accelerator protection.

## IV. ATTACK VECTORS

As shown in Figure 2, we categorize attacks to accelerator computing into three types: (1) attack on accelerator task (marked as  $A_T$ ) including the task code, data, metadata (e.g., task buffer pointer), page tables, and other task resources stored in host or accelerator memory, and (2) attack on accelerator environment (marked as  $A_E$ ) including the accelerator software, Memory Mapped I/O (MMIO) registers, and hardware device, and (3) attack on authenticity (marked as  $A_A$ ). All three types of attack are executed whether the victim task is in the host (i.e., task preparation/termination stage) or in the accelerator (i.e., task computing stage).

### A. Attacks in Task Preparation/Termination

In the task preparation or termination stage, the victim task (with input data or execution results) is stored in hostside memory and has yet to interact with the accelerator. We elaborate on the three types of attacks in this stage as follows.

To leak the sensitive data, the adversary may directly attack the victim task via the compromised host OS  $(A_{T1})$  or hypervisor  $(A_{T2})$ . To achieve this, the adversary aims to

Table III: Security solutions comparison among accelerator TEEs.

| _       |           | CVM/Er        | ıclave      | TSM  | Firmware  | CPU HW    | Bus | Enc. Module  | Attest Module | Acc. Controller | At       | tacks in ' | fask Pre | paration/ | Terminat | tion     |          |          |          | Attac    | ks in Tas | k Comp   | ating    |          |          |               |

|---------|-----------|---------------|-------------|------|-----------|-----------|-----|--------------|---------------|-----------------|----------|------------|----------|-----------|----------|----------|----------|----------|----------|----------|-----------|----------|----------|----------|----------|---------------|

| _ :     | Solutions | Acc. Workload | Acc. Driver | 1331 | riiiiware | CI O II W | Bus | Elic. Module | Attest Module | Acc. Controller | $A_{T1}$ | $A_{T2}$   | $A_{T3}$ | $A_{E1}$  | $A_{E2}$ | $A_{A1}$ | $A_{T4}$ | $A_{T5}$ | $A_{T6}$ | $A_{T7}$ | $A_{T8}$  | $A_{E3}$ | $A_{E4}$ | $A_{E5}$ | $A_{E6}$ | $A_{A2}$      |

| _       | $S_{AC1}$ | /             |             |      |           |           |     |              |               |                 | •        | •          | 0        | 0         | 0        | 0        | •        | •        | 0        | 0        | 0         | 0        | 0        | 0        | -0       |               |

| 2       | $S_{AC2}$ | /             | /           |      |           |           |     |              |               |                 | •        | •          | 0        | •         | 0        | 0        | •        | •        | •        | 0        | 0         | 0        | 0        | 0        | 0        | $\overline{}$ |

| Ö       | $S_{AC3}$ |               |             | /    |           |           |     |              |               |                 | •        | 0          | 0        | •         | •        | 0        | •        | 0        | •        | 0        | 0         | •        | 0        | 0        | 0        |               |

| S       | $S_{AC4}$ |               |             |      | /         |           |     |              |               |                 | •        | •          | 0        | •         | •        | 0        | •        | •        | •        | 0        | 0         | •        | •        | 0        | 0        |               |

| 3       | $S_{AC5}$ |               |             |      |           |           | /   |              |               |                 | 0        | 0          | 0        | 0         | 0        | 0        | •        | •        | 0        | 0        | 0         | •        | •        | •        | 0        | $\overline{}$ |

| _       | $S_{AC6}$ |               |             |      |           |           |     |              |               | 1               | 0        | 0          | 0        | 0         | 0        | 0        | •        | •        | •        | •        | •         | •        | 0        | 0        | •        | 0             |

| 2       | $S_{ME1}$ | /             | /           |      |           | 1         | I I |              |               |                 | •        | •          | •        | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0         | •        | •        | •        | -0       | 0             |

| Ξ.      | $S_{ME2}$ |               |             |      |           |           |     | 1            |               |                 | 0        | 0          | 0        | 0         | 0        | 0        | •        | •        | •        | 0        | •         | 0        |          | 0        |          | $\overline{}$ |

| We      | $S_{ME3}$ |               |             |      |           |           | 1   |              |               |                 | 0        | 0          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | •        | 0         | 0        | 0        | 0        | 0        |               |

| - E     | $S_{AT1}$ |               |             |      |           | /         | 1   | 1            |               |                 | 0        | 0          | 0        | 0         | 0        | •        | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | -0       | •             |

| íg<br>Ú | $S_{AT2}$ | /             | /           |      |           |           |     | 1            |               |                 | 0        | 0          | 0        | 0         | 0        | •        | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0        | 0             |

| ttes    | $S_{AT3}$ |               |             |      |           |           |     |              | 1             |                 | 0        | 0          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0        | •             |

| _       | $S_{AT4}$ |               |             |      |           |           |     |              |               | 1               | 0        | 0          | 0        | 0         | 0        | 0        | 0        | 0        | 0        | 0        | 0         | 0        | 0        | 0        | 0        | •             |

$g_{12}^{-1}$ . Access control based on CPU TEE but not protecting accelerator software stacks.  $S_{AC2}^{-1}$ . Access control based on CPU TEE and protecting accelerator software stacks.  $S_{AC2}^{-1}$ . Access control based on TEE manager (e.g., RMM) or secure hypervisor.  $g_{12}^{-1}$ . Access control based on firmware (e.g., excess) control based on EE manager (e.g., RMM) or secure hypervisor.  $g_{12}^{-1}$ . Access control based on Environment (e.g., excess) control based on accelerator hardware (e.g., excess) control based on Environment (e.g., excess) and authenticated kernel (e.g., kernel caller [65]).  $g_{12}^{-1}$ . Entrolbe based on CPU TEE  $g_{12}^{-1}$ . Attestation based on CPU TEE  $g_{12}^{-1}$ . Attestation based on Software  $g_{12}^{-1}$ . Attestation based on Experiment (e.g., kernel caller [65]).  $g_{12}^{-1}$ . Attestation based on Experiment (e.g., excess)  $g_{12}^{-1}$ . Attestation based on EXPUTE (e.g., EXPUTE)  $g_{12}^{-1}$ . Attestation based on Software  $g_{12}^{-1}$ . Attestation based on extension hardware with HROT.  $g_{12}^{-1}$ . Attestation based on Experiment (e.g., excess)  $g_{12}^{-1}$ . Attestation based on EXPUTE (e.g., EXPUTE)  $g_{1$

compromise the confidentiality or integrity of the victim's task. By compromising privileged software, adversaries can directly access the sensitive data (e.g., input, parameters, and execution results) or code of the victim task. Besides compromising task confidentiality, the adversary can threaten task integrity. The adversary can achieve this by replacing the input data of the victim task or by changing or injecting malicious code into the victim tasks. The adversary can achieve the attacks above by using the controlled Direct Memory Access (DMA)capable peripherals. In addition, the adversary may modify the page table and metadata (e.g., buffer pointer and page table pointer) of the victim task, misleading the accelerator to access incorrect data buffers or compute with malicious codes. Besides the software attacks, the adversary may launch the aforementioned attacks with physical assists  $(A_{T3})$ , such as extracting sensitive data from host DRAM or replaying the outdated execution results.

The adversary may compromise the accelerator runtime with two types of attack: (1) interfering with the functionality of accelerator software  $(A_{E1})$  and (2) performing Iago attacks  $(A_{E2})$ . For  $A_{E1}$  attack, the adversary may compromise the task scheduling to provide the incorrect task execution order, such as shuffling the execution order of tasks, arbitrarily replaying task execution, dropping tasks in confidential applications, or terminating the victim task ahead. Also, the adversary may compromise the memory management of accelerator software, such as interfering with the memory allocation for task buffers and page tables, tampering with the page table mapping (e.g., duplicated mapping or mapping to an unprotected region) in the victim task. For  $A_{E2}$  attack, the adversary may provide an incorrect value to TEE to mislead the accelerator protection. For instance, the adversary may give an incorrect page table or metadata address of the victim task, misleading the TEE to protect an unexpected region. The adversary may also replay the outdated data in the register to mislead the accelerator computation.

In addition, the adversary may compromise the authenticity of the victim task  $(A_{A1})$ . In the preparation stage of accelerator TEEs, the adversary may provide CVM/enclaves with incorrect task resources (i.e., data and task model).

#### B. Attacks in Task Computing

In task computing stage, the victim task is moved from the host to the accelerator-side memory. In this stage, accelerator software usually interacts with accelerators via MMIO. We elaborate on the three types of attacks in this stage.

The adversary may attempt to directly access or tamper with the victim task in the accelerator with the host OS  $(A_{T4})$  or the hypervisor  $(A_{T5})$  privilege. Although such an attack can be challenging on dedicated-memory accelerators (e.g., NVIDIA GPUs [14]) due to hardware isolation, it is more feasible to attack unified-memory accelerators (e.g., Arm GPUs [16]) that share the same memory with the host. Moreover, the adversary may abuse the accelerator TEEs and compromise the task isolation inside the accelerator  $(A_{T6})$ . For instance, the adversary may concurrently run an evil task with a victim task on the same accelerator. This evil task can monitor the execution of the victim task or directly access the victim task with modified page table mapping. A physical adversary can directly access the I/O bus (such as the PCIe I/O bus, shown in  $A_{T7}$ ) or accelerator-side memory  $(A_{T8})$  to leak or tamper with the sensitive task. Moreover, the adversary may tamper with the metadata or page table contents to achieve the same attacks as those on the host.

The adversary may access the accelerator MMIO on the host via OS  $(A_{E3})$  or hypervisor  $(A_{E4})$ , compromising the accelerator runtime during the accelerator TEE computing. Through MMIO, the adversary may change the register values of critical accelerator registers (e.g., page table base registers). Also, since several registers are delegated to control the accelerator computing, the adversary may send illegal execution commands to these registers to early execute/terminate the victim task, or perform unauthorized data transmission between the host and accelerator. For a physical adversary, she can execute the attacks above through tampering with MMIO  $(A_{E5})$ , or even physically compromising the accelerator hardware  $(A_{E6})$ .

Lastly, the adversary may compromise the authenticity of the accelerator  $(A_{A2})$ . Specifically, she may route the victim tasks to an unexpected or emulated device, monitoring the computing of the victim tasks.

Table IV: Access control solutions preference among accelerator TEEs.

|                            |                                                            | 1          | A         | ccess Con | trol Soluti | on        |           |                     | Acc. TEE Type                                                   |                |                                                          |

|----------------------------|------------------------------------------------------------|------------|-----------|-----------|-------------|-----------|-----------|---------------------|-----------------------------------------------------------------|----------------|----------------------------------------------------------|

| Scenario                   | Deployment Features                                        | $S_{AC1}$  | $S_{AC2}$ | $S_{AC3}$ | $S_{AC4}$   | $S_{AC5}$ | $S_{AC6}$ | Host-type           | Acctype                                                         | Mix-type       | Specific Mechanism                                       |

| (e.g., cloud)              | CPU with Any TEE (e.g., TDX/SEV for Multi-tenants)         | •          | 0         | 0         | 0           | 0         | •         |                     | [34] [51] [70]<br>[45] [46] [72]<br>[35] [54] [42]<br>[43] [76] |                | Intel SGX, Hardware-based Acc. Controller(Acc.)          |

| oi.                        | Re-programmed Acc.                                         | l          |           |           |             |           |           |                     | [65]                                                            |                | Intel SGX, Kernel Caller(Acc.)                           |

|                            | (e.g., FPGA for designer,<br>Hopper GPU of NVIDIA)         | 1 0        | •         | 0         | 0           | 0         | •         |                     | [58] [50] [79]                                                  |                | CVM with MEE, NVIDIA CC hardware-supported (Acc.)        |

| Acc.                       | Hopper GPU of NVIDIA)                                      |            |           |           |             |           |           |                     | [59]                                                            |                | Intel TDX/AMD SEV, Security Manager(Board)               |

| CPU-Discrete               | Plug-and-play Link                                         | 0          | •         | 0         | 0           | •         | •         |                     |                                                                 | [56] [57] [55] | TDISP                                                    |

| Disc                       | (e.g., PCIe-based Sec. HW)                                 | 1 0        | •         | 0         | 0           | •         | 0         | [33]                |                                                                 |                | Intel SGX, PCIe Root Complex                             |

| Ę                          |                                                            |            |           |           |             |           |           |                     | [30] [78]                                                       |                | Any CPU TEE, Security Controller(Ext. IO)                |

| ō                          | CPU with Specific TEE                                      | •          | 0         | •         | 0           | 0         | 0         | [61]                |                                                                 |                | AMD SEV, SVSM                                            |

|                            | (e.g., VMX root of Intel)                                  |            |           |           |             |           |           | [82]                |                                                                 |                | Intel SGX/TDX, VMX root                                  |

|                            | Legacy Acc.<br>(e.g., A100)                                | I <u> </u> | •         | •         |             | 0         | 0         | [47]                |                                                                 |                | Arm TrustZone, S-Hyp                                     |

|                            | (e.g., A100)                                               | 0          | •         | •         | •           | 0         | 0         | [67]                |                                                                 |                | Arm CCA, RMM, Monitor                                    |

|                            | Legacy CPU<br>(e.g., w/o CPU TEE)                          |            | 0         | 0         | 0           | 0         | •         |                     | [64] [48] [71]<br>[29] [81]                                     |                | Acc. Controller(Acc.)                                    |

|                            | Re-programmed Acc.                                         |            |           |           |             |           |           |                     | [62] [52]                                                       |                | Integrated Security Hardware(Board)                      |

|                            | Legacy CPU-Acc.                                            | 0          | 0         | 0         | 0           | •         | 0         |                     | [28]                                                            |                | PCIe-based Security Controller(Ext. IO)                  |

|                            | Preference                                                 | 14/34      | 12/34     | 4/34      | 1/34        | 6/34      | 26/34     | 5/34                | 26/34                                                           | 3/34           | Mainstream solution combination: $S_{AC1/2} + S_{AC5/6}$ |

| edge)                      |                                                            |            | 0         | 0         | •           | 0         | 0         | [68]                |                                                                 |                | Arm CCA, Monitor                                         |

| 8                          | Platform with specific sec. HW<br>(e.g., TZASC/GPC in Arm) | l          |           |           |             |           |           | [31] [63]           |                                                                 |                | Arm TrustZone/OP-TEE, Monitor                            |

| 5j)                        | or modified privilege SW                                   | I <u> </u> | •         | •         | 0           | 0         | 0         | [ <mark>77</mark> ] |                                                                 |                | Arm TrustZone, S-Hyp                                     |

| ,<br>,                     | (e.g., S-Hyp/                                              | <u> </u>   | •         | •         | •           | 0         | 0         | [80]                |                                                                 |                | Arm CCA, RMM, Monitor                                    |

| J-Ac                       | trusted firmware in Arm)                                   | 0          | •         | 0         | •           | 0         | 0         | [60] [32] [49]      |                                                                 |                | Arm TrustZone, Monitor                                   |

| Œ                          |                                                            | 0          | •         | 0         | •           | •         | 0         | [36] [69]           |                                                                 |                | Customized RISC-V TEE, M-Monitor, CPU IO Filter          |

| pet                        |                                                            | •          | 0         | 0         | •           | •         | 0         | [73]                |                                                                 |                | RISC-V Penglai, M-Monitor, CPU IO Filter                 |

| Integrated CPU-Acc. (e.g., | Re-programmed HW<br>(e.g., RISC-V/                         | •          | 0         | 0         | •           | 0         | •         |                     |                                                                 | [37]           | RISC-V Penglai, M-Monitor, Isolator, Guard(Acc.)         |

| Ē                          | FPGA-based DNN Acc.)                                       | i 0        | _         | 0         | 0           | 0         | _         |                     | [53]                                                            |                | Intel SGX, Memory Controller(Acc.)                       |

|                            |                                                            |            | •         |           | 0           | 0         | _         |                     | [75] [44] [74]                                                  |                | OP-TEE, Acc. Controller(Acc.)                            |

|                            | l i                                                        | 0          | 0         | 0         | 0           | 0         | •         |                     | [66]                                                            |                | Acc. Controller(Acc.)                                    |

|                            | Preference                                                 | 5/17       | 11/17     | 2/17      | 11/17       | 3/17      | 6/17      | 11/17               | 5/17                                                            | 1/17           | Mainstream solution combination: $S_{AC1/2} + S_{AC4}$   |

#### V. ACCESS CONTROL

## A. Solutions for Access Control

$S_{AC1}$ : TEE without accelerator driver. Studies can reuse the CPU-side TEE, including heavyweight CVMs (e.g., CVMs in AMD SEV [61], Intel TDX [82], and Arm CCA [68]) or lightweight enclaves (e.g., enclaves in SGX [42], [65], [97] or RISC-V [37], [73], or OP-TEE in Arm [31], [63]), to protect the accelerator workloads with sensitive data/code in both task preparation/termination and computing stage. The workloads are stored in a secure memory with softwareor hardware-assisted isolation, restricting unauthorized access from Host OS  $(A_{T1})$  and hypervisor  $(A_{T2})$ . Moreover, for unified-memory accelerators that share the same memory with the host, this solution additionally protects tasks from the same adversary during the task computing stage (i.e.,  $A_{T4}$  and  $A_{T5}$ ).  $S_{AC2}$ : TEE with accelerator driver. Besides protecting the accelerator workloads, studies can further extend their CPUside TEE protection to software stacks of varied accelerators (e.g., GPUs [33], [36], [80], NPUs [53], or generic types of accelerators [55]–[57]), including the accelerator driver and user-layer libraries (e.g., CUDA [98] or OpenCL [99]). With TEE protection, the accelerator software can securely manage tasks and device status. This solution defends against the attacks in  $S_{AC1}$ . Additionally, it addresses the threats to accelerator software  $(A_{E1})$  and illegal access  $(A_{T6})$ .

$S_{AC3}$ : Hypervisor-based access control. Studies can leverage a hypervisor-layer software, such as a TSM (e.g., AMD SVSM [56], [61], Intel TDX module [57], and Arm secure hypervisor [47] and RMM [55], [67], [80]) to defend against attacks from a low-privileged adversary, such as Host OS or other CVM/enclaves. This type of solution is mainly achieved by configuring hypervisor-layer access control mechanisms, such as Stage-2 translation in MMU/IOMMU [100]. In the task preparation/termination stage, this solution prevents the

OS from accessing victim tasks in host memory  $(A_{T1})$  and compromising accelerator software  $(A_{E1})$ . Moreover, it can verify the exchanged data between the host and TEE to partially mitigate Iago attacks  $(A_{E2})$ . In the task computing stage, this solution prevents accessing victim tasks in the accelerator  $(A_{T4,6})$  or accessing MMIO  $(A_{E3})$ .

$S_{AC4}$ : Firmware-based access control. Studies can configure the highest-privilege firmware (e.g., Monitor [31], [63], [68] in Arm, and M-mode Monitor [36], [37], [73] in RISC-V) to manage access control against the compromised OS, illegal CVM/enclaves, and hypervisor via MMU, or even malicious peripherals via IOMMU. This is typically supported by an isolated and hardware-assisted security primitive, such as TZASC [90] or TZPC [101] in Arm TrustZone, GPC [91] in Arm CCA, and PMP [102] in RISC-V. This solution covers previous attack vectors (i.e.,  $A_{T1,2,4,5,6}$ ,  $A_{E1,2,3}$ ) and additionally prevents the hypervisor's access to the task in the accelerator  $(A_{T5})$  and MMIO  $(A_{E4})$ .

$S_{AC5}$ : Access control in IO Bus. Studies may customize access control in the bus connection between the CPU-side host and accelerator hardware, such as customizing the IO bus filter [73], adding a CPU bus filter [36], and monitoring PCIe switch [28]. To achieve this, studies may change the bus configuration, or introduce additional security hardware. This solution focuses on the attacks in task computing, effectively addressing the unauthorized access to tasks in accelerator  $(A_{T4,5})$  and filtering illegal MMIO configuration  $(A_{E3,4})$ . Moreover, the bus protection mechanism can filter the malicious MMIO configuration  $(A_{E5})$  and data leakage on the bus  $(A_{T7})$  from the physical adversary.

$S_{AC6}$ : Access control in accelerator. Studies can provide accelerator with a security controller, such as a customized security module in accelerator (e.g., command/control processor [34], [43], [58]) to provide a maximal access control

guarantee in task computing stage. It effectively addresses the data leakage from CPU-side adversary and the evil tasks  $(A_{T4,5,6})$  and partially mitigates the malicious MMIO status configuration  $(A_{T3,4,5})$ . Moreover, protection on the accelerator can defend against physical tampering of the accelerator memory  $(A_{T8})$  and other device components  $(A_{E6})$ .

# B. Insights on Access Control

IAC1: Deployment scenarios drive multi-solution combination. Access control is an essential security solution in accelerator TEE design. Table III shows that higher-privilege solutions (e.g.,  $S_{AC4,5,6}$ ) address unmitigated threats in lowerprivilege ones (e.g.,  $S_{AC1,2,3}$ ). However, existing studies typically combine multiple solutions instead of relying on a single option. A key reason lies in the deployment characteristics of different scenarios (detailed in Table IV). For cloud-equipped accelerator TEEs, they usually implement on Intel- and AMDbased clouds (with unmodifiable firmware) and connect to discrete accelerators via external interfaces (e.g., PCIe). This makes the combination between CVM/enclave  $(S_{AC1,2})$  and accelerator-side defense  $(S_{AC5,6})$  — such as the hardware firewalls for NVIDIA H100 [58] — the mainstream choice. Such combination, however, can be constrained by the accelerator's programmability, motivating studies (e.g., XpuTEE [82]) to modify VMX Root to support legacy accelerators. Additionally, when the CPU lacks TEE support and the accelerator is non-programmable, efforts finally shift to modify PCIe I/O (e.g., HETEE [28]). For endpoint accelerator TEEs, the CPU and accelerators are typically integrated into Arm/RISC-V endpoint platforms. Studies tend to modify high-privilege software (e.g., secure hypervisor) and leverage existing security hardware (e.g., Arm TZASC or RISC-V PMP in monitor) to secure accelerators [31], [32], [49], [60], [68], [77], [80]. Overall, we recommend that TEE designers select hybrid access control solutions based on their specific scenarios.

IAC2: CPU-side TEE is not necessary for accelerator protection. Accelerator TEEs do not necessarily require CVM/enclave to secure accelerator software, or even the workload and environment. Instead, studies can integrate security checks/protection with privileged software or hardware within accelerator's workflow (e.g.,  $S_{AC3.4.5.6}$ ). As shown in Table IV, the number of studies based on  $S_{AC1}$  and  $S_{AC2}$ is comparable — 19 and 23 studies, respectively — and meanwhile 9 studies do not rely on TEE-based protections. A primary reason is that accelerator software can manipulate workloads (e.g., allocating memory) without accessing their exact contents. Thus, accelerator TEEs can implement full encryption for sensitive contents and optionally expose nonconfidential information (e.g., MMIO register values, page table, metadata) to the driver. Furthermore, removing accelerator software from CVM/enclave can effectively reduce their TCB size (will analyze in ITC1 and ITC2). Currently,  $S_{AC2}$  is only indispensable in specific cases, such as accelerator TEE with unmodifiable firmware/TSM/hardware or unchangeable software stacks.

IAC3: Overreliance on firmware-based solutions is infeasible. Accelerator TEEs cannot naively rely on firmwarebased access control  $(S_{AC4})$  to mitigate most attack vectors. A key reason is the significant granularity limitations of hardware-assisted security primitives. Table V illustrates these limitations for configurable security primitives (e.g., Arm TZASC [103], Arm GPC [85] and RISC-V PMP [104]) widely used in accelerator TEEs [31], [37], [63], [67], [73]. Specifically, most of them lack granularity support in two critical aspects: (1) limited and coarse-grained isolation, and (2) limited control over diverse access permission attributes both of which are essential for MMUs in commercial accelerators. Consequently, overreliance on  $S_{AC4}$ -based access control can severely disrupt the accelerator's functionality. This leads studies to reuse fine-grained access control mechanisms from TSMs or CVMs/enclaves.

Table V: Granularity comparison among security primitives.

|                        | Arm TZASC     | Arm GPC          | RISC-V PMP    | Addr Trans.            |

|------------------------|---------------|------------------|---------------|------------------------|

| Solution Type          | $S_{AC4}$     | $S_{AC4}$        | $S_{AC4}$     | $S_{AC1,2,3}$          |

| Minimal Granularity    | 32KB          | 4KB              | 4Byte         | 4KB                    |

| Configurable Regions   | Limited       | Non-limited      | Limited       | Non-limited            |

| Read/Write Distinction | Supported     | Not Supported    | Supported     | Supported              |

| Execute Permission     | Not Supported | Not Supported    | Supported     | Supported              |

| PAN/PXN Permission     | Not Supported | Not Supported    | Not Supported | Supported              |

| Studies Examples       | [31], [60]    | [67], [68], [80] | [37], [73]    | [31], [32], [47], [67] |

#### VI. MEMORY ENCRYPTION

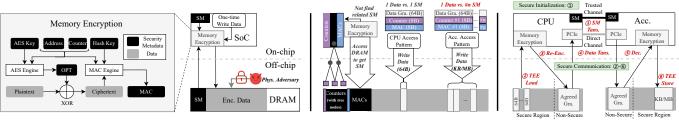

## A. Solutions for Memory Encryption

$S_{ME1}$ : CPU TEE-based memory encryption. Studies can reuse the CPU TEE-side software encryption API or memory encryption engines (e.g., Intel TME [87] in [57], AMD SME [2] in [56], [61], Arm MEC [85] in [67], [100]) to protect sensitive data/code in the CPU-side off-chip memory during the preparation stage. These sensitive workloads are encrypted in memory to restrict privileged adversaries (i.e.,  $A_{T2}$  and  $A_{T2}$ ) and physical adversaries (i.e.,  $A_{T3}$ ) from accessing plaintext. Moreover, for unified-memory accelerators that share the same memory with the host, this solution protects tasks from the same adversaries during the task computing stage (i.e.,  $A_{T4.5.6.7.8}$ ).

$S_{ME2}$ : Accelerator kernel/hardware-based memory encryption. Besides CPU-side encryption, studies can provide cryptographic support to the accelerator-side memory. They achieve this by delivering authorized en/decryption kernels [34], [50], [65] to the accelerator, or design hardware-based en/decryption engine [58], [59]. This solution effectively prevents physical adversaries (i.e.,  $A_{T8}$ ) from accessing data, and mitigates data leaks caused by CPU-side privileged adversaries (i.e.,  $A_{T4}$  and  $A_{T5}$ ) and malicious tasks (i.e.,  $A_{T6}$ ). To prevent physical adversaries from accessing confidential data (i.e.,  $A_{T7}$ ) on the external PCIe bus, this solution collaborates with  $S_{ME1}$  for encrypted data/code transmission.

$S_{ME3}$ : IO Bus-based memory encryption. Lastly, studies may deploy memory encryption mechanisms on the bus between the CPU and the accelerator. When transmitting accelerator tasks with sensitive data/code, this solution carefully encrypt the transmission packets between the CPU and accelerator devices. To achieve this, studies may apply an

(a) Basic memory encryption against physical adversary

(b) Comparison of access patterns under traditional memory encryption

(c) Data transfer protocol under incompatible encryption granularity

Figure 3: Memory encryption workflows of accelerator TEEs. Table VI: Security implications of missing memory encryption.

| Scenarios                        | Victim                                                         | Physical Threats   | Missing Memory Encryption $(S_{ME}) \rightarrow$ Consequence                                                                                                                          | Influenced Studies                                                                  |

|----------------------------------|----------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|                                  | Plug-and-play Host Memory<br>(e.g., DDRx)                      | $A_{T3}, A_{E5}$   | Missing CPU-based encryption $(S_{ME1}) \rightarrow \text{Data/code/metadata/PTEs}$ in plaintext on host memory are vulnerable to physical access/tampering (e.g., cold-boot attacks) | [28], [48] [47], [60]                                                               |

| CPU-Discrete Acc.                | 3D-stacked Acc. Memory<br>(e.g., HBM)                          | -                  | Missing any memory encryption $\rightarrow$ Minimal physical threats                                                                                                                  | [34], [42], [43] [52], [58]<br>[61], [62], [79] [71]                                |

| (e.g., cloud)                    | On-board Acc. Memory (e.g., GDDRx/LPDDRx) $A_{T8}$             |                    | Missing Accbased encryption $(S_{ME2}) \rightarrow \text{Data/code/metadata/PTEs}$ in plaintext on acc. memory are vulnerable to physical access/tampering (e.g., probing attacks)    | [28], [33], [35], [47], [55]–[57], [60]<br>[30], [65], [67], [72], [78], [82]       |

|                                  | Plug-and-play Link<br>(e.g., PCIe/CXL)                         | $A_{T7}$           | $\label{eq:missing IO-based (S_{ME3}) or CPU-Acc.\ encryption\ (S_{ME1,2}) \rightarrow Physical\ access/tamper/replay\ packets in plaintext on the link (e.g., replay\ attacks).}$    | [33], [47], [48], [82]                                                              |

| Integrated CPU-Acc. (e.g., edge) | On-board/Plug-and-play<br>Shared Memory<br>(e.g., LPDDRx/DDRx) | $A_{T3,8}, A_{E5}$ | Missing CPU-Accbased encryption $(S_{ME1,2}) \rightarrow \text{Data/code/metadata/PTEs}$ in plaintext on shared memory are vulnerable to physical access/tampering                    | [31], [32], [36], [49], [63], [68], [80]<br>[37], [44], [68], [73]–[75], [77], [80] |

Missing de/encryption engine (e.g., AES) for confidentiality  $\rightarrow$  Direct access to plaintext data Missing integrity check engine (e.g., Message Authentication Code, MAC) for integrity  $\rightarrow$  Tampering with plaintext/ciphertext data Missing number used once (e.g., counter/integrity tree [105]) for freshness  $\rightarrow$  Replay attacks

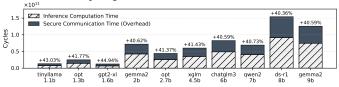

Table VII: Comparison of security metadata for accelerator TEE memory protection.