## FlushTime:

Towards Mitigating Flush-based Cache Attacks via Collaborating Flush Instructions and Timers on ARMv8-A

Jingquan Ge, Fengwei Zhang

Research Institute of Trustworthy Autonomous Systems. Southern University of Science and Technology

9<sup>th</sup> July. 2023

FlushTime

- Motivation

- 2 Threat Model and Assumptions

- 3 Our Solution: FlushTime

- 4 Security Analysis

- **5** Performance Evaluation

- **6** Conclusion

- Motivation

- Cache-related attack

- Flush-based cache-related attack

## Motivation

#### ARMv8-A CPU

- Cache-related attack Flush-based cache-related attack

## Why study ARMv8-A CPU?

- ARMv8-A-based devices (smart phones, tablet, vehicle systems and IoT ) have flooded the market.

- ARMv8-A cloud servers have begun to disrupt the data center market.

Motivation 000000000

#### Cache-related attack

Flush-based cache-related attack

### Cache-related attack

Motivation

- Increasing types of cache-related attacks have been presented by researcher since 1990s.

- With the continuous emergence of Meltdown, Spectre and their variants, cache-related attacks have become one of the biggest threats to modern processors and operating systems.

- Flush+Reload and Flush+Flush utilize cache flush instructions to reduce the noise and improve the resolution, called flush-based cache-related attack.

- Meltdown, Spectre and most of the discovered variants are also based on Flush+Reload.

- Motivation

- Cache-related attack

- Flush-based cache-related attack

### Why study Flush-based cache-related attack?

- Attackers only need to know target virtual addresses, physical address mapping is not required.

- Although the flush instructions greatly reduce the threshold of cache attacks. Prohibiting the flush instructions in user space is not feasible.

- It is an attractive topic to ensure the availability of cache flush instructions in user space while avoiding the security vulnerabilities posed by them.

10 / 45

- Motivation

- Cache-related attack

- Flush-based cache-related attack

- Hardware and software defense

## Defenses and their shortcomings

Threat Model and Assumptions

Motivation

000000000

- Modifications to the hardware architecture cannot be deployed on existing devices.

- Software runtime defenses cannot cover all flush-based cache-related attacks and may bring significant performance loss.

- Browser defense countermeasures disable high resolution time API, which is not feasible in the operating system.

Motivation

00000

2 Threat Model and Assumptions

Threat Model and Assumptions

- Security Assumptions Attacker capabilities

- Our Solution: FlushTime

- 4 Security Analysis

- 6 Performance Evaluation

- 6 Conclusion

1 Matination

00000

2 Threat Model and Assumptions

Security Assumptions

Threat Model and Assumptions

- Our Solution: FlushTime

- 4 Security Analysis

- 6 Performance Evaluation

- 6 Conclusion

# Security Assumptions

- Attackers can execute her code on the same machine with the victim process.

- There is shared memory between the attacker process and the victim process.

- Attackers do not have the root privilege and cannot use other attack methods to tamper with the kernel code or escalate privileges to obtain sensitive system information.

- Attackers do not have the ability to design an effective eviction strategy.

00000

2 Threat Model and Assumptions Attacker capabilities

Threat Model and Assumptions

## Attacker capabilities

- The attacker knows the source code and address layout of the victim process or kernel.

- Attackers can rely on the flush instructions to clean up the cache lines of the shared pages and leak information.

Research Institute of Trustworthy Autonomous Systems, Southern University of Science and Technology

- 3 Our Solution: FlushTime

- 3 Our Solution: FlushTime Overview of FlushTime

#### Overview of FlushTime

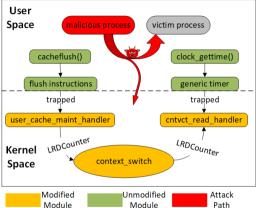

- FlushTime is a framework that can resist all flush-based cache-related attacks while ensuring the availability of flush instructions and generic timers on ARMv8-A.

- FlushTime utilizes the instruction/register trap mechanism of ARMv8-A to trap cache flush instructions and generic timer access into the kernel interrupt handlers.

- In the kernel space, these two handlers cooperate with each other to handle the interrupts. When a process calls a cache flush instruction, the time resolution obtained from the generic timer will be temporarily reduced.

#### Architecture of FlushTime

Figure 1: The architecture of FlushTime on ARMv8-A Linux. *LRDCounter* represents the low resolution delay counter, which counts the number of *context\_switch()* in low resolution state.

Research Institute of Trustworthy Autonomous Systems, Southern University of Science and Technology

- 3 Our Solution: FlushTime

Design of FlushTime

## Design of Flush Time

Threat Model and Assumptions

- Modify the default configuration of Linux to trap flush instructions and generic timer into the EL1 level (kernel space).

- Modify the interrupt handler of the flush instructions.

- Modify the context switch of the process.

- Modify the interrupt handler for accessing the generic timer.

# Handler Algorithms

Algorithm 1: user cache maint handler() in FlushTime

**Input:** Virtual address to be flushed: *vir addr*; **Output:** Low resolution delay counter: *LRDCounter*;

- 1 Flush the cache line of vir addr:

- <sup>2</sup> Store NumCSLR into LDRCounter:

- 3 Return to ELO:

- (a) Algorithm of flush instruction handler.

Algorithm 2: cntvct read handler() in FlushTime

**Input**: Low resolution delay counter: LRDCounter: Output: Time read from CNTVCT EL0: CNTVCTime:

- 1 Read CNTVCT EL0 into CNTVCTime:

- 2 if (LRDCounter!=0) then

- Reduce the resolution of CNTVCTime by NumLRMB bits:

- 4 end

- s else

- Keep the high resolution of CNTVCTime;

Research Institute of Trustworthy Autonomous Systems, Southern University of Science and Technology

- 7 end

- s Return CNTVCTime to EL0:

- (b) Algorithm of timer access handler

Figure 2: Algorithms of the two handlers

Research Institute of Trustworthy Autonomous Systems, Southern University of Science and Technology

- 3 Our Solution: FlushTime

- Relationship between Flush and Timer

## Relationship between flush instructions and generic timer

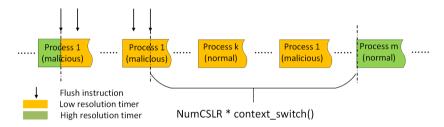

Figure 3: Relationship between flush instructions and generic timer when FlushTime is enabled. NumCSLR is the number of context\_switch() in low resolution state.

- Motivation

- ② Threat Model and Assumptions

- 3 Our Solution: FlushTime Overview of FlushTime Design of FlushTime Relationship between Flush and Time

- Implementation of FlushTime

- Security Analysis

- 6 Performance Evaluation

Our Solution: FlushTime

## Implementation of FlushTime

- Modify Linux boot function smp\_init().

- Modify the flush handler user\_cache\_maint\_handler().

- Modify process scheduling function *context\_switch()*.

- Modify generic timer handler *cntvct read handler()*.

- 1 Motivation

- 2 Threat Model and Assumptions

- 3 Our Solution: FlushTime

- 4 Security Analysis

Selection of NumLRMB and NumCSLE

Attack Results

- 6 Performance Evaluation

- 6 Conclusion

- Motivation

- 2 Threat Model and Assumptions

- Our Solution: FlushTime

- 4 Security Analysis

Selection of NumLRMB and NumCSLR

Attack Results

- 6 Performance Evaluation

- 6 Conclusion

Security Analysis

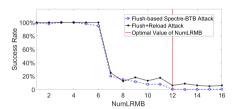

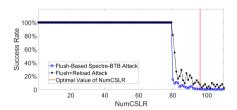

(a) The relationship between the parameter NumLRMB and attack success rate on TaiShan 200 server. Both the two attacks are multi-process attacks that execute 100 processes. The red line represents the optimal value of NumLRMB.

(b) The relationship between the parameter NumCSLR and attack success rate on TaiShan 200 server. Both the two attacks are multi-process attacks that execute 100 processes. The red line represents the optimal value of NumCSLR.

Figure 4: The relationship between the two parameters and attack success rate.

Motivation

Table 1: Selection of NumLRMB and NumCSLR on different hardware platforms.

Security Analysis

| Platform        | # ARMv8-A cores | NumLRMB | NumCSLR |

|-----------------|-----------------|---------|---------|

| TaiShan 200     | 96              | 12      | 96      |

| Raspberry Pi 4B | 4               | 14      | 4       |

| ZCU102          | 4               | 15      | 4       |

- 4 Security Analysis Attack Results

Security Analysis 00000000

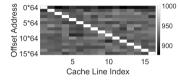

#### Flush+Reload attack results

(a) Flush+Reload attack on original Linux without any defenses.

(b) Flush+Reload attack when flush instructions and generic timer are trapped into EL1.

(c) Flush+Reload attack when FlushTime is enabled (NumCSLR=96). The resolution of the generic timer is reduced by 12 bits in real time (NumLRMB==12).

Figure 5: Flush+Reload attacks on different system setups. It is a multi-process attack that execute 100 processes. The depth of the color corresponds to the number of cache hits in 1000 AES T-Table encryptions.

### Flush+Flush attack results

(a) Flush+Flush attack on original Linux without any defenses.

(b) Flush+Flush attack when flush instructions and generic timer are trapped into EL1.

(c) Flush+Flush attack when FlushTime is enabled (NumCSLR=96). The resolution of the generic timer is reduced by 12 bits in real time (NumLRMB==12).

Figure 6: Flush+Flush attacks on different system setups. It is a multi-process attack that execute 100 processes. The depth of the color corresponds to the number of cache hits in 1,000 AES T-Table encryptions.

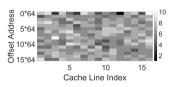

### Spectre-BTB attack results

FFFFFFFFFF मममम स'स'स'स FFFF  $\mathbf{F}\mathbf{F}\mathbf{F}\mathbf{F}$  $\mathbf{F}\mathbf{F}\mathbf{F}$  $\mathbf{F}\mathbf{F}\mathbf{F}$ FF E'E FFF E'E'E प्रप्रप्रम  $\mathbf{F}'\mathbf{F}'\mathbf{F}'\mathbf{F}'$ समसम स स स स स 4444444444

(a) Spectre-BTB attack on original Linux without any defenses.

**чччччччччч**ч ਜ'ਜ'ਜ'ਜ ччччч ਜ਼-ਜ਼-ਜ਼-ਜ਼ म'म'म  $\mathbf{F}\mathbf{F}\mathbf{F}$ FFF ਜਾਜ FF  $\mathbf{F}\mathbf{F}\mathbf{F}$ FFF म'म'म'म ਜ ਜ ਜ ਜ न'न'न'न'न मन्यम्ब यसम्बन्धसम्बन्धसम्बन

(b) Spectre-BTB attack when flush instructions and general timer are trapped into EL1.

(c) Spectre-BTB attack when FlushTime is enabled (NumCSLR==96). The resolution of the generic timer is reduced by 8 bits in real time (NumLRMB==8).

when FlushTime is enabled (NumCSLR==96). The resolution of the generic timer is reduced by 12 bits in real time (NumLRMB==12).

(d) Spectre-BTB attack

Figure 7: Spectre-BTB attacks on different system setups. It is a multi-process attack that execute 100 processes. '?' represents a character that has not been cracked.

- Motivation

- 2 Threat Model and Assumptions

- Our Solution: FlushTime

- 4 Security Analysis

- **5** Performance Evaluation

Performance of instructions and APIs

System Performance (UnixBench)

User Application Performance (SPEC\_CPU 2017)

- Motivation

- 2 Threat Model and Assumptions

- Our Solution: FlushTime

- 4 Security Analysis

- 5 Performance Evaluation

Performance of instructions and APIs

System Performance (UnixBench)

User Application Performance (SPEC\_CPU 2017)

## Flush Instructions, Generic Timer and Time API

Table 2: Average time delay of calling flush instructions, calling API and accessing generic timer.

| Instruction, API or | Original Linux time | FlushTime enabled  |  |

|---------------------|---------------------|--------------------|--|

| timer               | delay (cycle)       | time delay (cycle) |  |

| CNTVCT_EL0          | 12.14               | 27.73 (127%)       |  |

| clock_gettime()     | 103.02              | 115.29 (19%)       |  |

| DC CIVAC            | 38.21               | 28.15 (-26%)       |  |

| DC CVAU             | 69.33               | 26.98 (-61%)       |  |

| DC CVAC             | 69.58               | 28.11 (-60%)       |  |

- Motivation

- 2 Threat Model and Assumptions

- Our Solution: FlushTime

- 4 Security Analysis

- **5** Performance Evaluation

Performance of instructions and APIs

System Performance (UnixBench)

User Application Performance (SPEC\_CPU 2017)

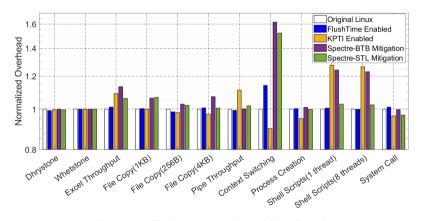

### UnixBench results

Figure 8: Evaluation results of UnixBench.

- Motivation

- 2 Threat Model and Assumptions

- Our Solution: FlushTime

- 4 Security Analysis

- **5** Performance Evaluation

Performance of instructions and APIs System Performance (UnixBench)

User Application Performance (SPEC\_CPU 2017)

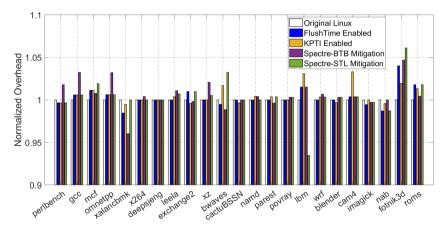

# SPEC\_CPU 2017 results

Figure 9: SPEC2017 benchmark results.

- Motivation

- 2 Threat Model and Assumptions

- Our Solution: FlushTime

- 4 Security Analysis

- Performance Evaluation

- **6** Conclusion

43 / 45

#### Conclusion

- FlushTime does not need to modify the hardware, which is easy to deploy on existing devices.

- FlushTime not only partially prevents instructions and timers from being

maliciously exploited by flush-based cache-related attacks, but also ensures their

availability in a normal system.

- Security and performance evaluation on the real hardware platform shows that FlushTime is not only more secure than other software solutions, but also has the lowest performance overhead.

Q&A